Today AMD finally releases their Milan-X CPUs with 3D V-Cache. SemiAccurate told you most of the details weeks ago but now we can add the last few bits.

Today AMD finally releases their Milan-X CPUs with 3D V-Cache. SemiAccurate told you most of the details weeks ago but now we can add the last few bits.

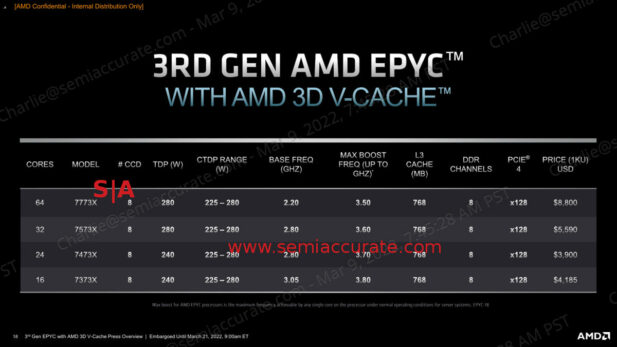

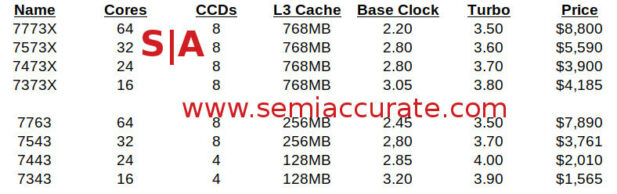

Lets start out with the SKUs AMD is releasing, the same four we told you about a couple of months ago. Not much to add on this other than the price is a bit lower in some places than SemiAccurate expected, but more on that later.

The official Milan-X details

As we said in February, Milan-X is a drop in replacement for Milan, it shows up as the same chip with a bigger L3. To be fair you might need a BIOS update but that is about as much as you will need to do to get ready for these parts. L3 cache goes up from Milan’s 256MB to 768MB with Milan-X. Things get a bit more interesting when you look at what they are replacing, or at least branching out from. The table below has the most comparable mainstream Milan-non-X parts, we don’t think the -F high frequency SKUs are going to be cross-shopped much with -X.

AMD Milan vs Milan-X

There are two main differences, the CCD count goes down on the mainstream parts but doesn’t go down on the Milan-X parts for obvious reasons. The other odd bit is that the 16C 7373X costs $285 more than the 24C 7473X. This is entirely due to the fact that a lot of HPC workloads, EDA, CFD, and FAE for example, love large caches but run software priced by the core count they run on. With cache:core ratios being paramount in this space, more boxes with few cores is often a lot more cost effective than a single node with a high core count CPU. More on this later.

You will also notice that clocks go down quite a bit on the higher core count SKUs but less so on the lower end parts. For base clocks this is entirely due to TDP, the extra cache uses power and that drops the base clock 250MHz on the 64C parts, quite reasonable. The mid-range drop is much less pronounced and that is mainly due to the TDP of the -X parts being 225-280 across the board versus as low as 165-200 for the 16C 7343. Speed costs energy.

More interesting is the peak turbo clocks which hardly budge, down 100MHz for three of the four SKUs. With the same cores and a higher TDP, this seems curious but has a likely technical explanation, insulation. Since the cache and the spacers are on top of the core die/CCD, they insulate it quite nicely and add a bit of heat to boot. That brings up the question about what AMD did with the construction of the 3D V-Cache itself.

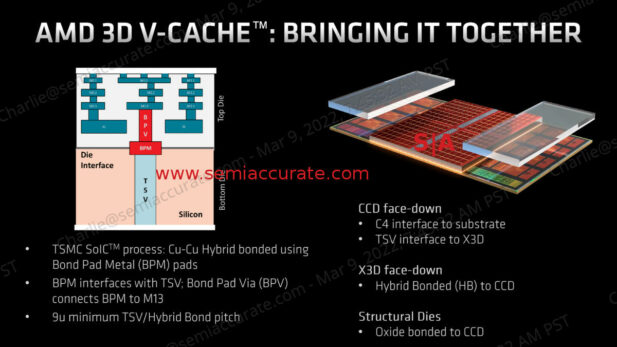

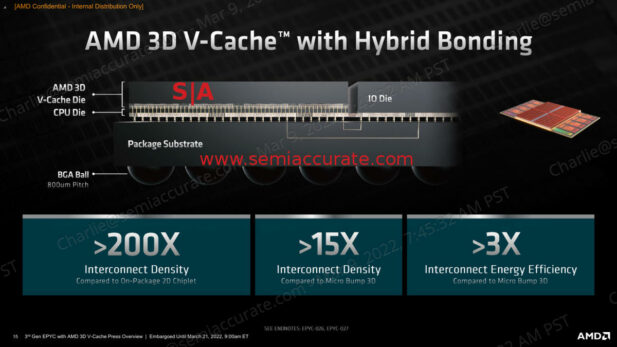

AMD Milan-X die construction

As you can see, AMD takes a slice of cache made on the same 7nm silicon process as the main CCD, and bonds it to the center of the CCD. The new slice has 64MB of cache compared to the 32mb of the main die but only takes half of the area. This is because the cache die doesn’t have the ring bus or the control mechanisms of the CCD’s cache but it still has the bit cells, tag arrays, and LRU structures. This allows them to make a very dense structure that is about half the size of the CCD itself.

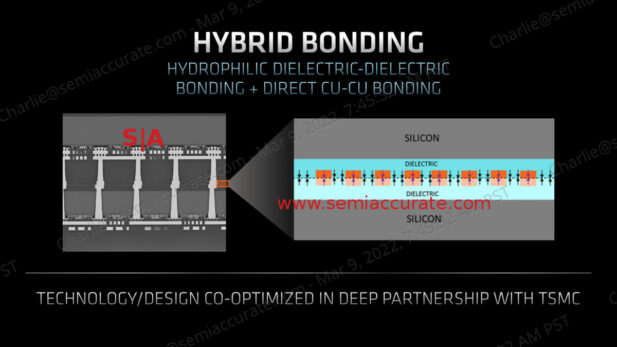

Milan-X hybrid bonding process

The bonding process is really interesting too and SemiAccurate has hinted about it in the past. You take the two die and bond the silicon/non-metal, copper to be precise, bits together chemically. Once the die are bonded you then anneal it to connect the copper pads electrically and off you go. The silicon spacers on the edges of the die are oxide bonded down, a much simpler process. The take home message? It is complex to bond delicate structures with a 9µ bump pitches but AMD is doing it in volume so I guess the process is working well.

Milan-X die thickness diagram

The last bit is interesting because of the thickness, or lack thereof, of the dies. Skipping the marketing numbers, take a look at the left side of the diagram. The IOD is full height, actually very thin but still as high as the CCD and cache stack combined. As an aside you don’t want to have differing die heights, it makes the thermal cap construction problematic as Intel found out in the 45/32nm days. In any case if the diagram is to be believed, AMD has thinned the CCD down quite a bit on the V-Cache models and the cache die itself is slimmed a little too. Nothing good or bad here unless yields are impacted but interesting from a technical perspective.

That brings us to the analysis and there are two obvious questions. First is why AMD is putting Milan-X out now, it makes little sense to do. Then there is the issue of pricing and what it intones about AMD’s near future direction. Pricing is obviously tied into the question of why but the implications are possibly quite profound.

Note: The following is for professional and student level subscribers.

Disclosures: Charlie Demerjian and Stone Arch Networking Services, Inc. have no consulting relationships, investment relationships, or hold any investment positions with any of the companies mentioned in this report.

Charlie Demerjian

Latest posts by Charlie Demerjian (see all)

- Nuvia Founders Have A New Startup, Nuvacore - Apr 16, 2026

- Nvidia Is Negotiating To Buy A Large PC Oriented Company - Apr 13, 2026

- Dell Does Modular Laptop Boards Right - Apr 7, 2026

- Qualcomm Snapdragon X2 Review Embargo Lifts Tomorrow Morning - Apr 6, 2026

- Intel Cuts HDR OLED Panel Power with SmartHDR - Apr 2, 2026