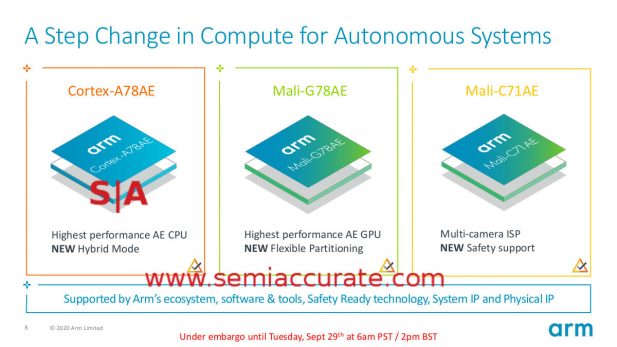

![]() ARM is releasing a trio of automotive and safety modified IP cores today, each significantly changed from their vanilla namesakes. SemiAccurate thinks the Cortex-A78AE is the most interesting but the Mali-G78AE and Mali-C71AE have some new twists too.

ARM is releasing a trio of automotive and safety modified IP cores today, each significantly changed from their vanilla namesakes. SemiAccurate thinks the Cortex-A78AE is the most interesting but the Mali-G78AE and Mali-C71AE have some new twists too.

I’ll bet you thought SemiAccurate was joking when we asked if you had your fill of industry standard safety acronyms and certifications when we talked about Intel’s new embedded offerings last week. This time around ARM has a trio of new automotive parts, the A78AE, G78AE, and C71AE, some of which can be safety certified all the way up to ASIL D/SIL 3 should you have the free time to do the paperwork. Truly exciting stuff if you are in the embedded, safety, or automotive worlds, but if you are not, these three have some interesting twists anyway.

Welcome our three new ARM IP blocks

But wait you say, your thirst for obscure industry safety acronyms unsatisfied, what if you need ISO 26262 or IEC 61508 features to support either ASIL B/SIL 2 or ASIL D/SIL 3? (Author’s Note: You can look all this up on your own, you are a capable person and we trust your research skills) In that case you need the new Cortex-A78AE which is a claimed 30% faster than the older A76AE. But raw speed is less important that safety features in this arena, and that is where this new CPU core gets interesting with the new Hybrid Mode.

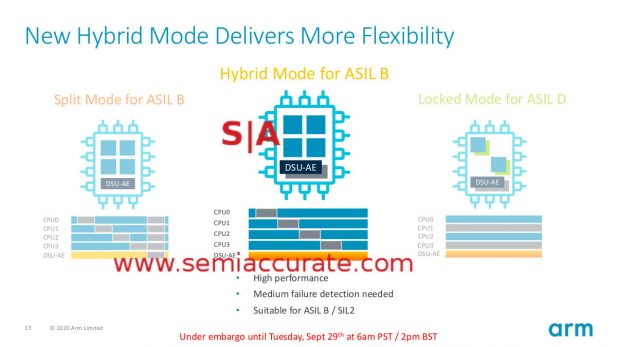

Hybrid mode splits the difference

To reach ASIL B, you need to have a CPU that does periodic health checks on itself. The old A76AE could do this with a so called Split Mode where each of the cores operates independently and takes itself off line every so often for a health check. The DSU-AE (DynamIQ Shared Unit) also took a break as well at which point the whole device was unavailable. This isn’t a massive performance drop, ARM says 0-2% in their testing but it is still a hit. That said it gets you the capability of ASIL B/SIL 2 so it is worth the overhead. Also recall that the ratings are for end devices, not cores/IP, so ARM provides the documentation and tracing to those aiming for the certs, but can’t get you the end cert itself.

If you need ASIL D/SIL 3 ratings, Split modes are not good enough, not even close. For this you need Locked Mode where cores operate in pairs running in lockstep. The DSU-AE is also running in lockstep and the comparisons are all done in hardware. This is a great thing for the software developers, they don’t need to know the lockstep exists much less that it is running. The down side is that while everything is much safer, it takes a 50% speed hit for effectively running the same code twice, plus low single digit overhead for the lockestep mode.

But wait we hear you cry, all the cool kids in school want ASIL B/SIL 2 capabilities but don’t want the periodic down time of the DSU-AE self-check, is there any hope for them? As long as they are sporting the new A78AE, the answer is yes! You just double up your DSU-AE resources and run that in lockstep while all the cores are running in split mode, something ARM calls Hybrid Mode for obvious reasons. Hybrid mode is a little ‘safer’ than Split Mode while offering some of the lockstep advantages with the slightly lower overhead of Split Mode. It won’t hit ASIL D/SIL 3 but it will make those cool kids happy.

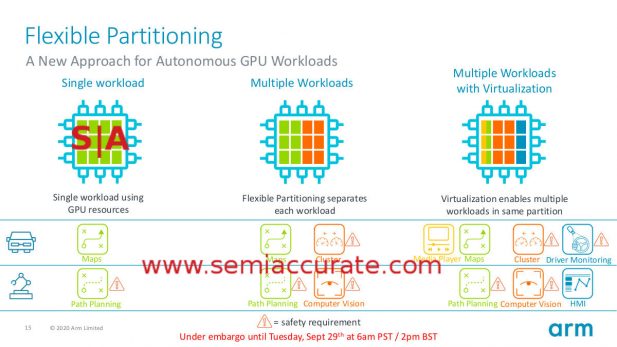

The new Mali-G78AE is ARM’s first safety capable GPU and for the acronym starved will support ISO 26262, IEC 61508, and ASIL B/SIL 2. Like the non-AE version of the G78, it will support up to 24 cores and has all he features of the consumer parts plus a new one, partitioning. And lockstep. Don’t forget self-test, interface parity, separation, isolation checks, and memory protection either, they matter to the people giving out those safety stickers. Luckily ARM documents all of this to ease getting of those stickers for the end devices, that part matters a lot to the developers and saves them enormous amounts of time and money.

How to split up a Mali-G78

While many of the features listed above are micro-architectural, partitioning is more of big feature add. The G78AE can be partitioned in several ways, in hardware at the four shader cluster level, so a maximum of six partitions per GPU. You can always make a GPU with less than four shaders per cluster for more granularity but, umm, that would be a bit silly. If you want more granularity you can virtualize the shaders themselves and split things that way but brings with it a bunch of safety certification concerns. In the end, stick with hardware for safety critical uses, virtualize away in software for everything else, and you can do both on the same GPU at the same time as long as it is a Mali-G78AE.

But what if you need to capture images and analyze them, and do so safely? You know for things like self-driving cars, rear view cameras to replace mirrors, and death-bots that terminate the right people without much indiscriminate carnage? For that you need a safety capable ISP and guess what, ARM has one of those now too, the Mali-C71AE to be specific. While there are a lot of spiffy features, they all fail to reach the bar of spiffy features that can be shown in a spiffy diagram. Sorry. That said you will be happy to hear the C71AE can also hit ISO 26262, IEC 61508, and ASIL B/SIL 2, yay!

As you would expect, this ISP can support up to four cameras in realtime or 16 buffered ones in memory. Either way it will max out at 1.2Gpps but each pixel supports ultra-wide dynamic range so there are a lot of bits moving through the silicon. On top if this there is a tone mapping engine which will come in really handy for things like reversing into sunlight with a child hiding in the shadows, now the death-bots won’t… umm… you can avoid the child with your car.

What makes the Mali-C71AE worthy of the AE suffix, other than it was designed to be safety aware at the circuit level? Many more functions are CRC covered and many blocks are covered by continuous self-checks like the other two new IP blocks released today. Software delivered with the core can also provide realtime diagnostics for each part of the pipeline as well. The coolest feature however is that software can initiate the injection of diagnostic frames into the video streams so if you see things like this on your screens, don’t worry, it is normal system functions doing their job.

In a nutshell, that is what ARM is delivering today for the automotive, industrial robotics, and death-bot world. Each of these -AE IP blocks, the A78AE, G78AE, and G71AE, are all built from the ground up for safety critical applications and come with all the documentation needed to ease the regulatory burden and speed time to market. Don’t discount how valuable this is for the embedded world, this is a key selling point for in that space. With these three new blocks, ARM takes a big step toward providing all the pieces for a full safety critical pipeline.S|A

Charlie Demerjian

Latest posts by Charlie Demerjian (see all)

- Nuvia Founders Have A New Startup, Nuvacore - Apr 16, 2026

- Nvidia Is Negotiating To Buy A Large PC Oriented Company - Apr 13, 2026

- Dell Does Modular Laptop Boards Right - Apr 7, 2026

- Qualcomm Snapdragon X2 Review Embargo Lifts Tomorrow Morning - Apr 6, 2026

- Intel Cuts HDR OLED Panel Power with SmartHDR - Apr 2, 2026