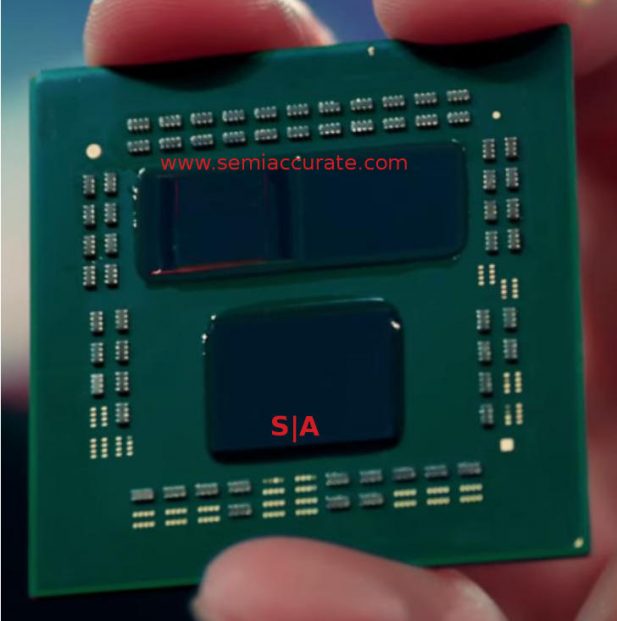

AMD just vaulted back into the advanced packaging lead last night with their 3D V-Cache technology. SemiAccurate will try to explain why this is several steps beyond what others have done or even shown off.

AMD just vaulted back into the advanced packaging lead last night with their 3D V-Cache technology. SemiAccurate will try to explain why this is several steps beyond what others have done or even shown off.

Show me the cache money!

History Lesson:

AMD is often credited as being the first to the mass market with a 2.5D packaging product on their Fiji GPU in 2015. It uses HBM memory on a passive silicon interposer, basically a giant CPU without transistors. It may be picking nits but Xilinx got there several years before with their big Virtex FPGAs but those are at a slightly different price point. The take home message here is that silicon on silicon packaging has been around for a while and AMD is the clear leader in making volume 2.5D devices at mass market price points. No one else has done so as consistently and cost effectively.

Moving on to less advanced technology, AMD went to MCMs or Multi-Chip Modules in 2017 with Naples and then on to chiplets in 2019 with Rome, both server products that sold tens of millions of devices. On the consumer side the big Ryzens from the Rome generation also used the same tech and sold an order of magnitude more chips.

The problem with both MCMs and chiplets are they are old tech, MCMs have been around since the dawn of time and are old hat. AMD used them with devastating effectiveness in the market but that was due to intelligent planning and looking at the big picture, the classic thinking outside the box. They used the tools they had well rather than doing something technically new. While you could argue that the chiplets in Rome are a new idea, it is a stretch.

Competition:

Mindshare in the advanced packaging world has been sucked up by Intel of late with their two leading technologies, Foveros and EMIB. Both are really interesting, effective, and probably don’t do what you think they do. Neither are the killer tech that will punt any competitors into the weeds either, but they are solid if used appropriately. The key here is scope and how large some want you to think it is.

EMIB stands for Embedded Multi-Die Interconnect Bridge and it is rather unique. If you look at AMD’s Fiji in the link above, you will see that the interposer is huge, it is bigger than the footprint of the GPU and HBM stacks plus all the whitespace. That size silicon, even on an old process with only a few metal layers, is not cheap, nor is the assembly. Since silicon on silicon means low or no thermal expansion mismatches that drop yield and kill chips, it tends to be a smart way to design things.

The idea behind EMIB is to take a thin slice of interposer material, basically a wire made from a chip, and embedded it in the standard green organic PCB that a CPU or MCM is normally mounted on. The cost of the package goes up by a bit and the assembly gets a little trickier but the cost of the ‘interposer’ goes way down. In short you only pay for the interposer where you need it and nowhere else. In theory it is a much better way to go.

The problem here is that you have thermal expansion mismatches between the organic materials and the silicon that interposers avoid. This is likely a minor problem for cost and yield, one that Intel has likely solved through careful engineering. Another problem is alignment, it is harder to assemble dies on mismatched substrates, but again this is a problem Intel appears to have solved.

One problem that is more fundamental to EMIB is multi-hop packages, basically a device that has a die <-> EMIB <-> die <-> EMIB <-> die structure. Each link has error margins and they add up with each hop, additive errors get painful very quickly. To date Intel has only talked about a single product, the Stratix 10 GX 10M FPGA, that uses a highly complex multi-hop configuration. Since the 2019 ‘launch’ there have been no pictures that SemiAccurate has seen of working silicon nor is it actually for sale as far as we can tell. Yes there are web pages about it but our sources in the FPGA world have not been able to find one in the wild.

EMIB is the better way in theory. In the real world, depending on the complexity of the device, it may be the better way too. The more complex your device, the more yield and assembly losses you have and somewhere along the way you cross over the point where interposers are cheaper and more effective. This point likely changes with each new device so what was the right way last week may not be today. The take home message here is that EMIB is not the killer app, it is useful but not a clean kill by any means.

Foveros:

Foveros is the other drum Intel has been banging on advanced packaging, and with good reason. It was first shown off in late 2018 on a prototype Lakefield SoC. That said, forget about the chip for now, lets look at the construction. Foveros is the Intel name for face to face packaging (F2F) technology and it is impressive. Instead of using TSVs (Through Silicon Vias) for 3D packaging, Foveros just flips one die and bonds it to the one below. This means it is cheaper to make, you lose less area to TSVs, and you avoid the yield losses from drilling thousands of holes in your die.

The down side is that with Foveros you can only stack two dies, with TSVs you can theoretically go as high as you want. Foveros also avoids the additive error problems of multi-die stacks so yields should be higher, or at least the assembly loss mitigations will be less onerous. The price for this simplicity is obviously lack of scale but it is otherwise a great way to go.

Power is the big problem with Foveros, by putting an active die on an active die you are putting two heat sources, the transistors, between two insulators, the silicon. Normally much of the heat from a chip is pulled off through the metal layers and pins, something that is much harder to do in a F2F device. This is why Intel has only shown off low power devices using Foveros.

Overall Foveros works and Lakefield has been shipping for over a year now but in very low volumes. This points to high cost and low yields, something that doesn’t inspire confidence that Foveros bearing devices will be suited for consumer volumes. Once again this is an engineering challenge that can be overcome, just realize that with what has been shown so far, it is still an open question.

Power Power Power:

Assembly, yield, and cost are big problems with these advanced technologies but they are all engineering issues that can and mostly have been overcome over the years. Power and it’s attendant heat is one that has not been overcome yet, at least to the degree that some would like you to believe. AMD’s interposer and chiplet devices have their high power silicon dies spread out on the package. Nvidia’s disastrous first attempt at interposers and HBM had lower yields than even the first Fermi’s due to missing engineering basics.

Intel’s EMIB and Foveros have a lot of PR behind them and there are real products on the market too. All are low volume proof of concept more than mass market products though, none of them come close the the lowest volume AMD advanced packaging products. That said they all are lower power or use spread out dies in the case of EMIB. To date no one has released a high power product that doesn’t use spread out chips no matter what the tech. Most will talk and intone it is not an issue, especially to the less technical listener, but the tech isn’t there to make real products yet.

Enter AMD Again:

So that brings us back to AMD and their Computex 2021 keynote speech. In short AMD just kicked all other comers to the curb with their technology even if they didn’t call it out explicitly. What they did is a game changer but not the holy grail of advanced packaging technology. Think of it as a big step that will pay significant dividends in the market. Once again no one else has shown anything close and AMD is planning on starting consumer volume production this year.

Lets take a look at what AMD announced, why it is so impressive, and why no one else is close.

Note: The following is for professional and student level subscribers.

Disclosures: Charlie Demerjian and Stone Arch Networking Services, Inc. have no consulting relationships, investment relationships, or hold any investment positions with any of the companies mentioned in this report.

Charlie Demerjian

Latest posts by Charlie Demerjian (see all)

- Nuvia Founders Have A New Startup, Nuvacore - Apr 16, 2026

- Nvidia Is Negotiating To Buy A Large PC Oriented Company - Apr 13, 2026

- Dell Does Modular Laptop Boards Right - Apr 7, 2026

- Qualcomm Snapdragon X2 Review Embargo Lifts Tomorrow Morning - Apr 6, 2026

- Intel Cuts HDR OLED Panel Power with SmartHDR - Apr 2, 2026